2002 May 22 12

Philips Semiconductors Product specification

Low power audio DAC UDA1334BT

Notes

1. All supply connections must be made to the same external power supply unit.

2. At 3 V supply voltage, the input pads are TTL compatible. However, at 2.0 V supply voltage no TTL levels can be

accepted, but levels from 3.3 V domain can be applied to the pins.

3. When the DAC drives a capacitive load above 50 pF, a series resistance of 100 Ω must be used to prevent

oscillations in the output operational amplifier.

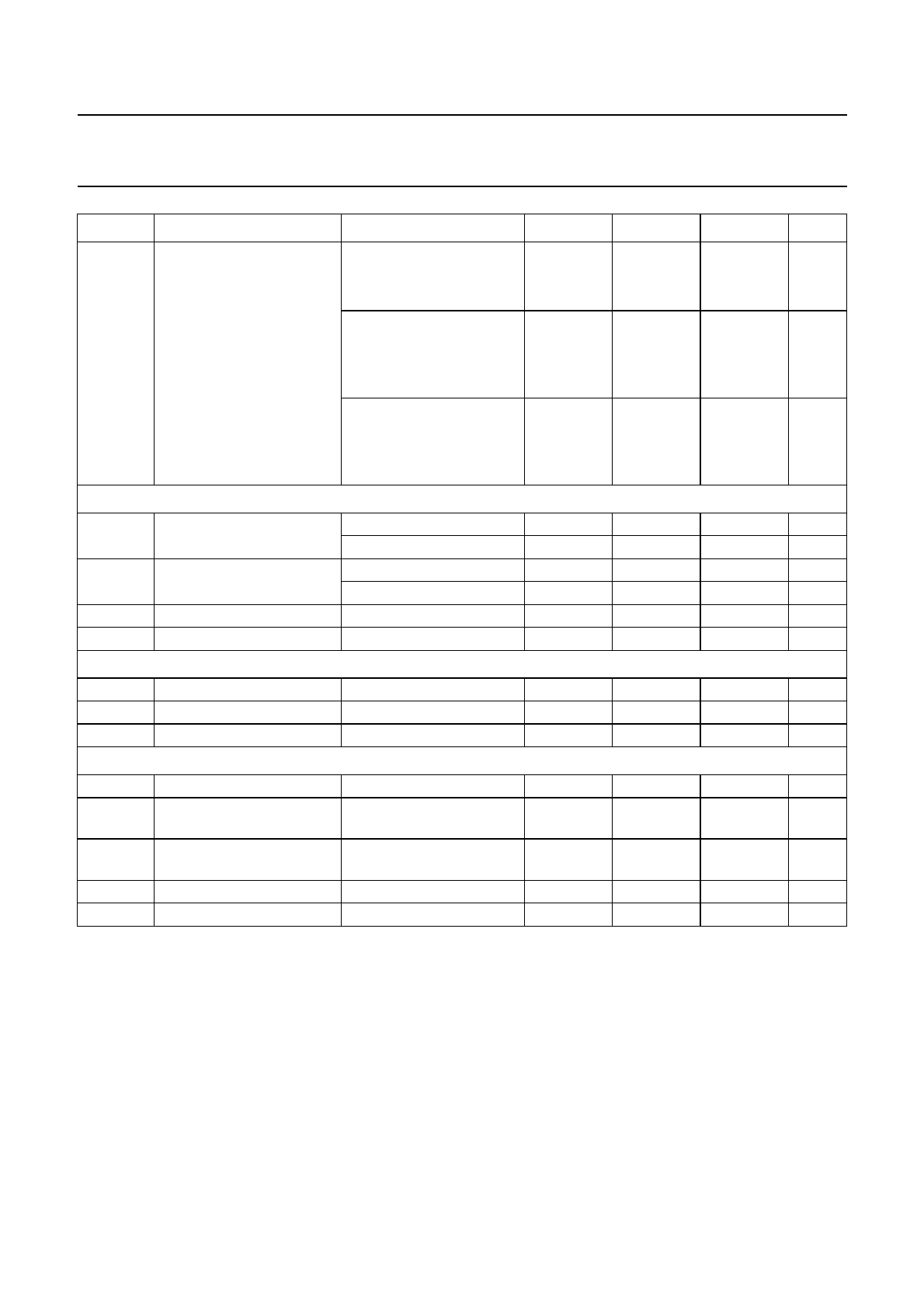

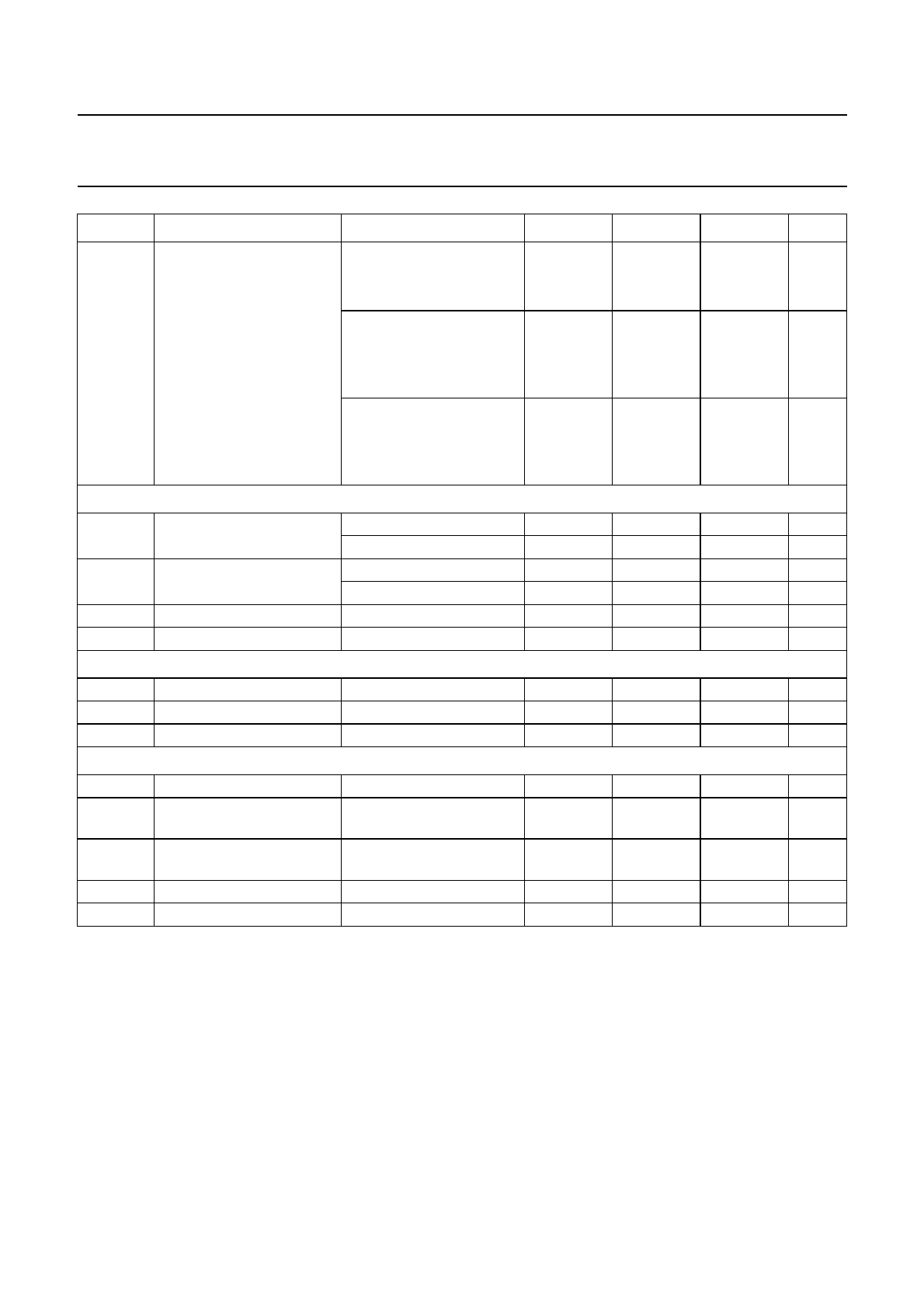

I

DDD

digital supply current normal operating mode

at 2.0 V supply voltage − 1.4 − mA

at 3.0 V supply voltage − 2.1 − mA

Sleep mode;

at 2.0 V supply voltage

clock running − 250 −µA

no clock running − 20 −µA

Sleep mode;

at 3.0 V supply voltage

clock running − 375 −µA

no clock running − 30 −µA

Digital input pins; note 2

V

IH

HIGH-level input voltage at 2.0 V supply voltage 1.3 − 3.3 V

at 3.0 V supply voltage 2.0 − 5.0 V

V

IL

LOW-level input voltage at 2.0 V supply voltage −0.5 − +0.5 V

at 3.0 V supply voltage −0.5 − +0.8 V

I

LI

input leakage current −−1µA

C

i

input capacitance −−10 pF

3-level input: pin PCS

V

IH

HIGH-level input voltage 0.9V

DDD

− V

DDD

+ 0.5 V

V

IM

MID-level input voltage 0.4V

DDD

− 0.6V

DDD

V

V

IL

LOW-level input voltage −0.5 − +0.5 V

DAC

V

ref(DAC)

reference voltage with respect to V

SSA

0.45V

DDA

0.5V

DDA

0.55V

DDA

V

R

o(ref)

output resistance on

pin V

ref(DAC)

− 25 − kΩ

I

o(max)

maximum output current (THD + N)/S < 0.1%;

R

L

= 800 Ω

− 1.6 − mA

R

L

load resistance 3 −−kΩ

C

L

load capacitance note 3 −−50 pF

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT