KP915GV Product Manual

104

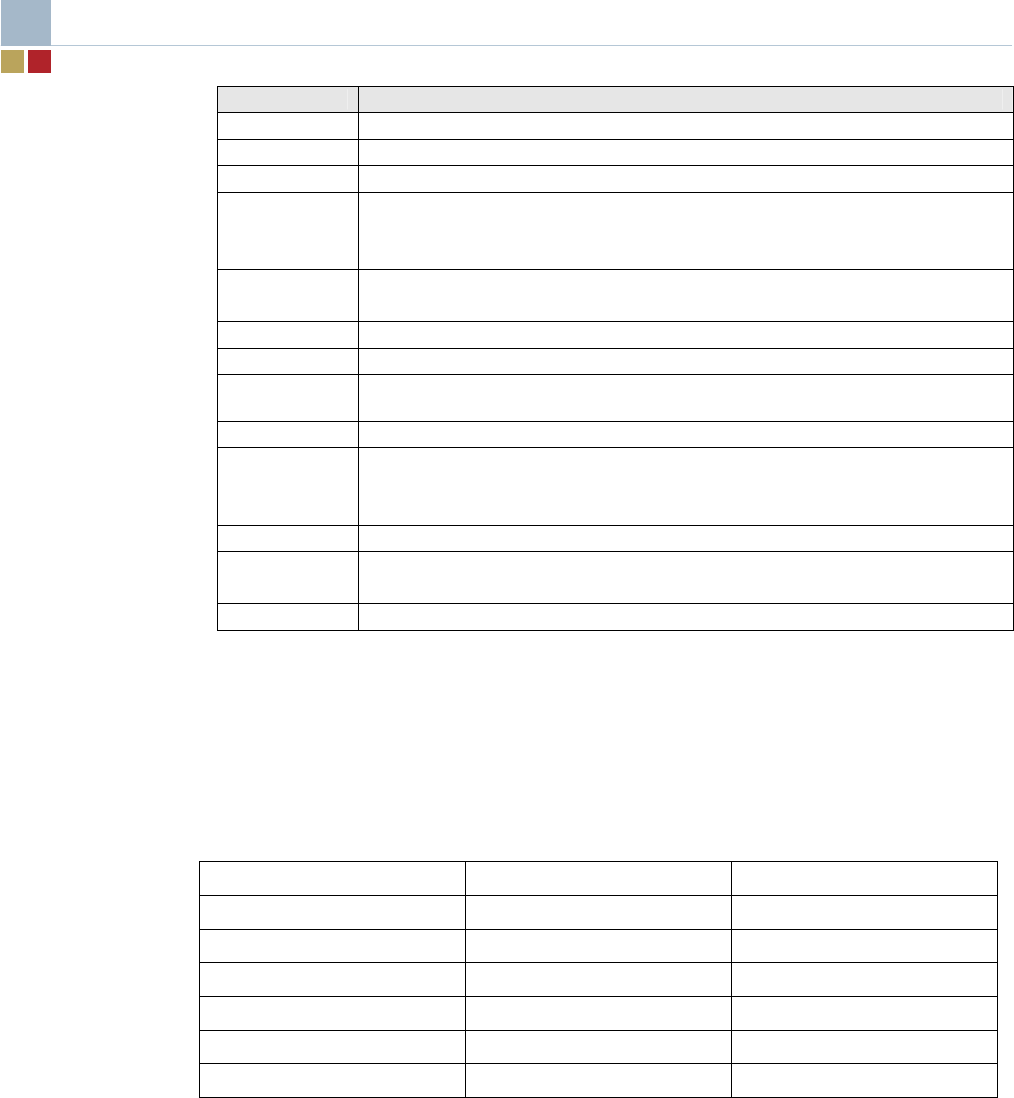

POST Code Description

75h Detect & install all IDE devices: HDD, LS120, ZIP, CDROM…

77h Detect serial ports & parallel ports.

7Ah Detect & install co-processor

7Fh Switch back to text mode if full screen logo is supported.

82h Call chipset power management hook. If password is set, ask for password.

83h Save all data in stack back to CMOS

84h Initialize ISA PnP boot devices

85h USB final Initialization.

93h Read HDD boot sector information for Trend Anti-Virus code

94h

Enable L2 cache Program boot up speed Chipset final initialization. Power

management final initialization Clear screen & display summary table.

95h Program daylight saving Update keyboard LED & typematic rate

96h

Build MP table Build & update ESCD Set CMOS century to 20h or 19h Load

CMOS time into DOS timer tick Build MSIRQ routing table.

FFh Boot attempt (INT 19h)

4.18 POST Beep

• A single long beep followed by two short beeps. It indicates that a video error has occurred

and the BIOS cannot initialize the video screen to display any additional information.

• A single long beep repeatedly. This indicates that a DRAM error has occurred.

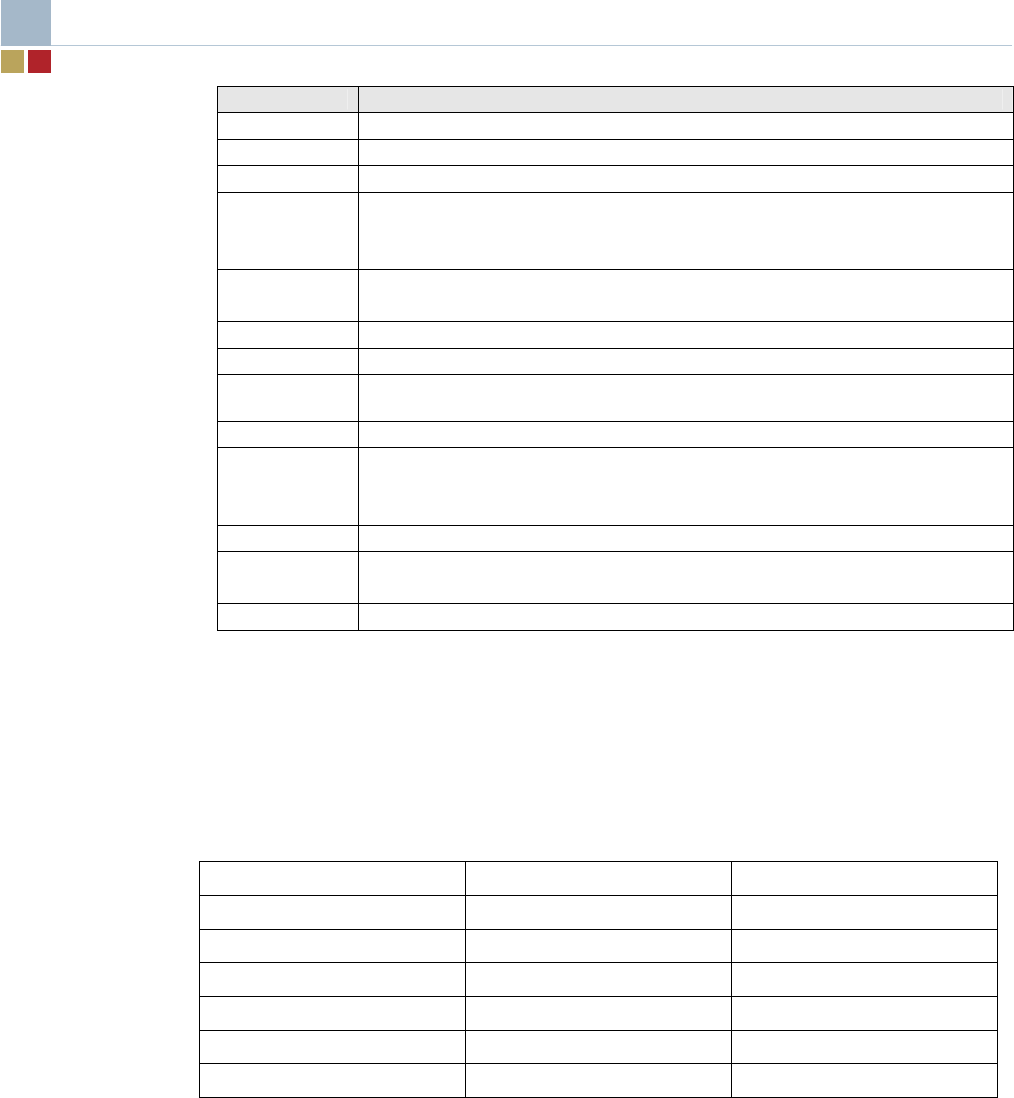

4.19 SMBus Device Configuration

Device Name Address Description

Channel A DIMM1 A0 DDR2 Memory

Channel A DIMM2 A8 DDR2 Memory

Channel B DIMM1 A4 DDR2 Memory

Channel B DIMM2 AC DDR2 Memory

ICS 954101AFT D2 & D3 CK410E

NS LM96000 5C Hardware Monitor