KP915GV Product Manual

109

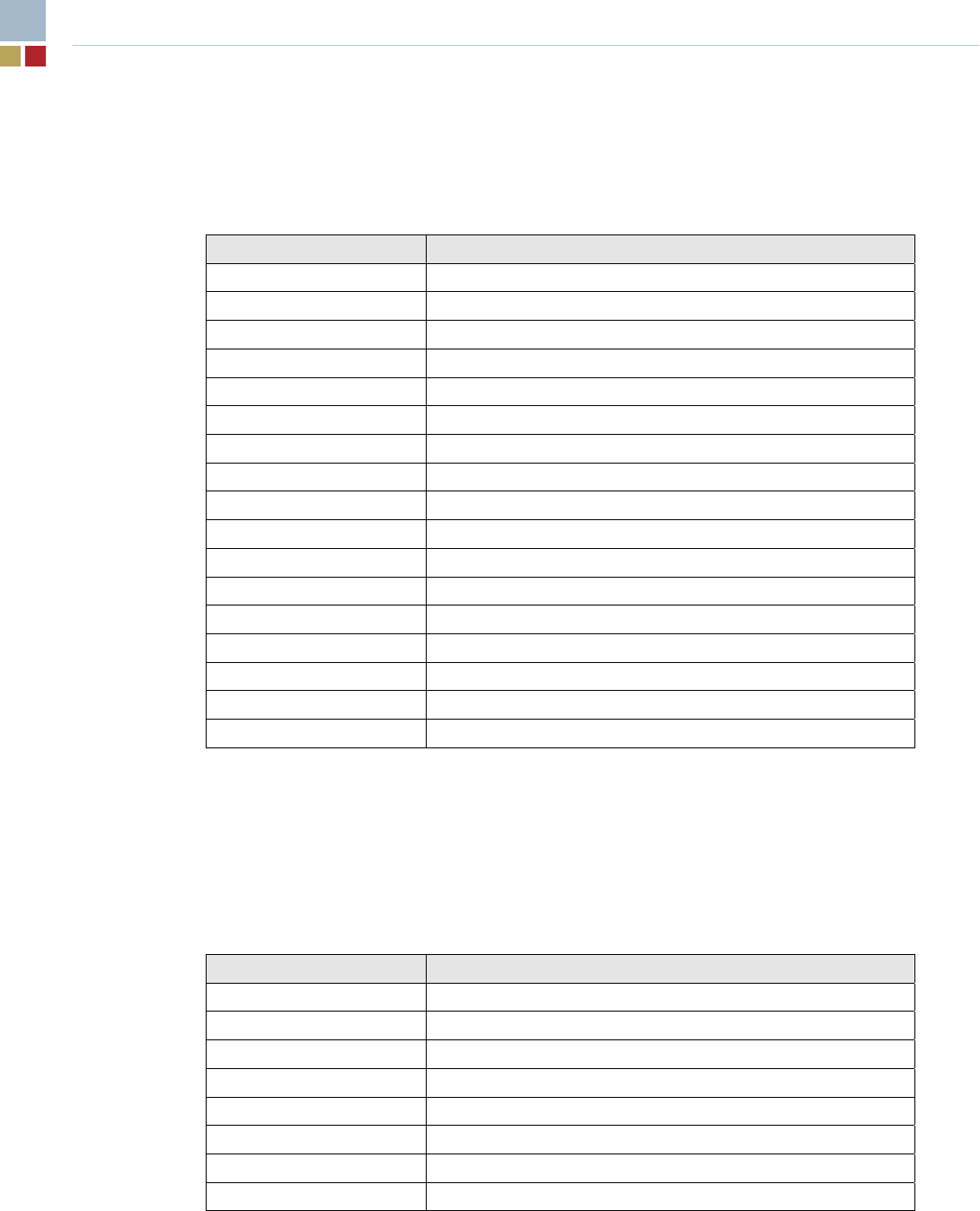

A.5 ISA Interrupt Allocation

While the motherboard does not include an ISA bus, it includes an ISA-compatible interrupt

controller (PIC) in order to be compatible with AT standard architecture. The interrupts are

allocated as described in the next table.

Table 12. ISA Interrupt Allocation

Interrupt Description

IRQ0 System Timer

IRQ1 Keyboard Controller

IRQ2 Cascade interrupt

IRQ3 COM2, COM1 or unassigned

IRQ4 COM1, COM2 or unassigned

IRQ5 Parallel port or unassigned

IRQ6 Floppy

IRQ7 Printer port or unassigned

IRQ8 Real time clock/CMOS RAM

IRQ9 ACPI SCI (when configured for ACPI operating system)

IRQ10 Unassigned

IRQ11 Unassigned

IRQ12 PS/2 mouse or unassigned

IRQ13 Floating point unit

IRQ14 Primary IDE or unassigned

IRQ15 Secondary IDE or unassigned

NMI PCI PERR and SERR signals

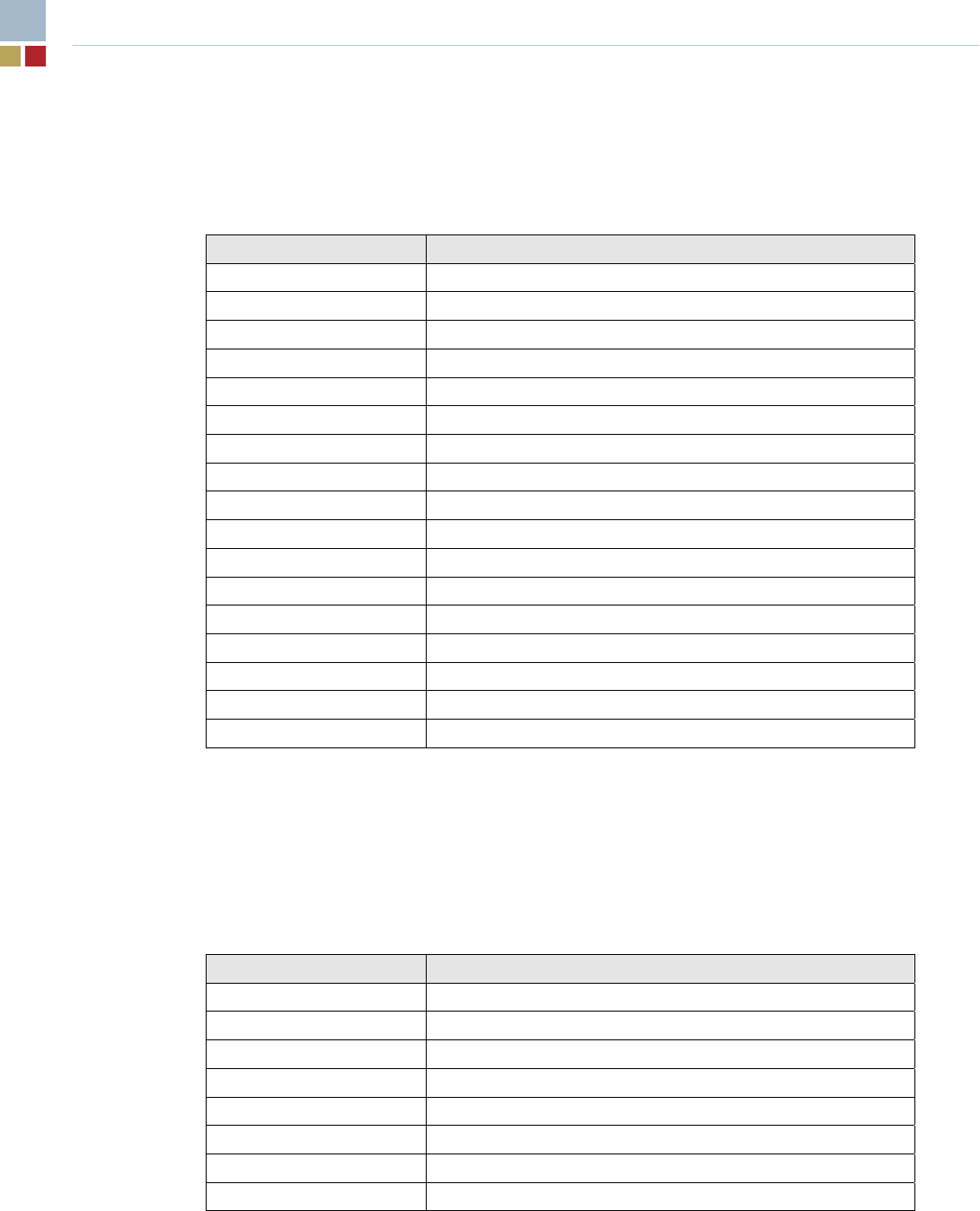

A.6 ISA DMA Channel Allocation

While the motherboard does not support an ISA bus, it includes an ISA-compatible DMA controller

in order to be compatible with AT standard architecture. The DMA channels are allocated as

described in the next table.

Table 13. ISA DMA Channel Allocation

DMA Channel Description

Channel 0 Unassigned 8-bit channel

Channel 1 Unassigned 8-bit channel

Channel 2 Floppy controller or unassigned 8-bit channel

Channel 3 ECP parallel port or unassigned 8-bit channel

Channel 4 Cascade channel

Channel 5 Unassigned 16-bit channel

Channel 6 Unassigned 16-bit channel

Channel 7 Unassigned 16-bit channel